日前台积电全球技术论坛如期举行,论坛上除了分享正在量产的5nm工艺以外,还透露了第二代5nm、4nm等先进工艺方面的信息,但在5nm已经投产的情况下,外界更期待的其实是5nm之后的下一个全新工艺节点3nm工艺。

台积电透露,和第一代5nm工艺相比,3nm工艺将使芯片的性能提升10%到15%,能耗则可以降低25%到30%,台积电还承诺3nm工艺的晶体管密度将是5nm工艺的1.7倍。按照计划,3nm工艺将在明年进入风险试产,2022年下半年大规模量产。

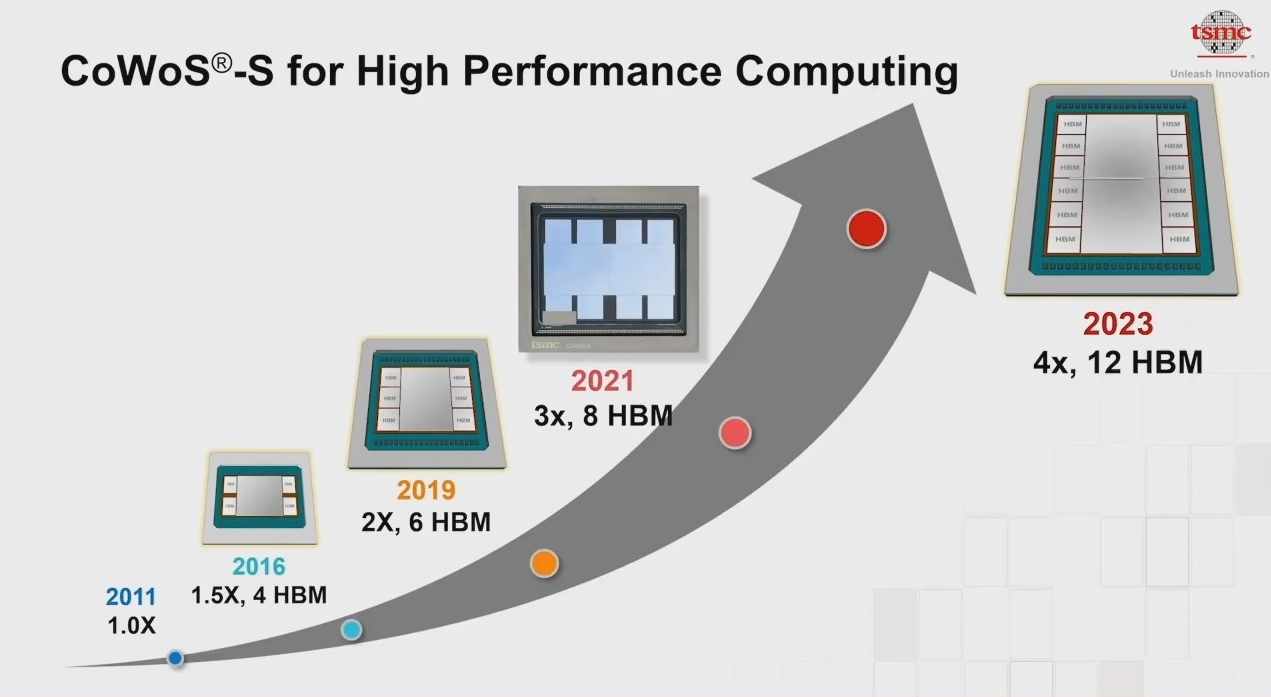

但台积电明显察觉到了一个新的问题,随着高性能计算需求的与日俱增,还有半导体工艺的日益复杂,未来单靠升级制程工艺升级,肯定是无法解决所有问题的,还需从最根本的封装技术上多下一些功夫,CoWoS-S晶圆级封装技术其实已经使用很多年了。

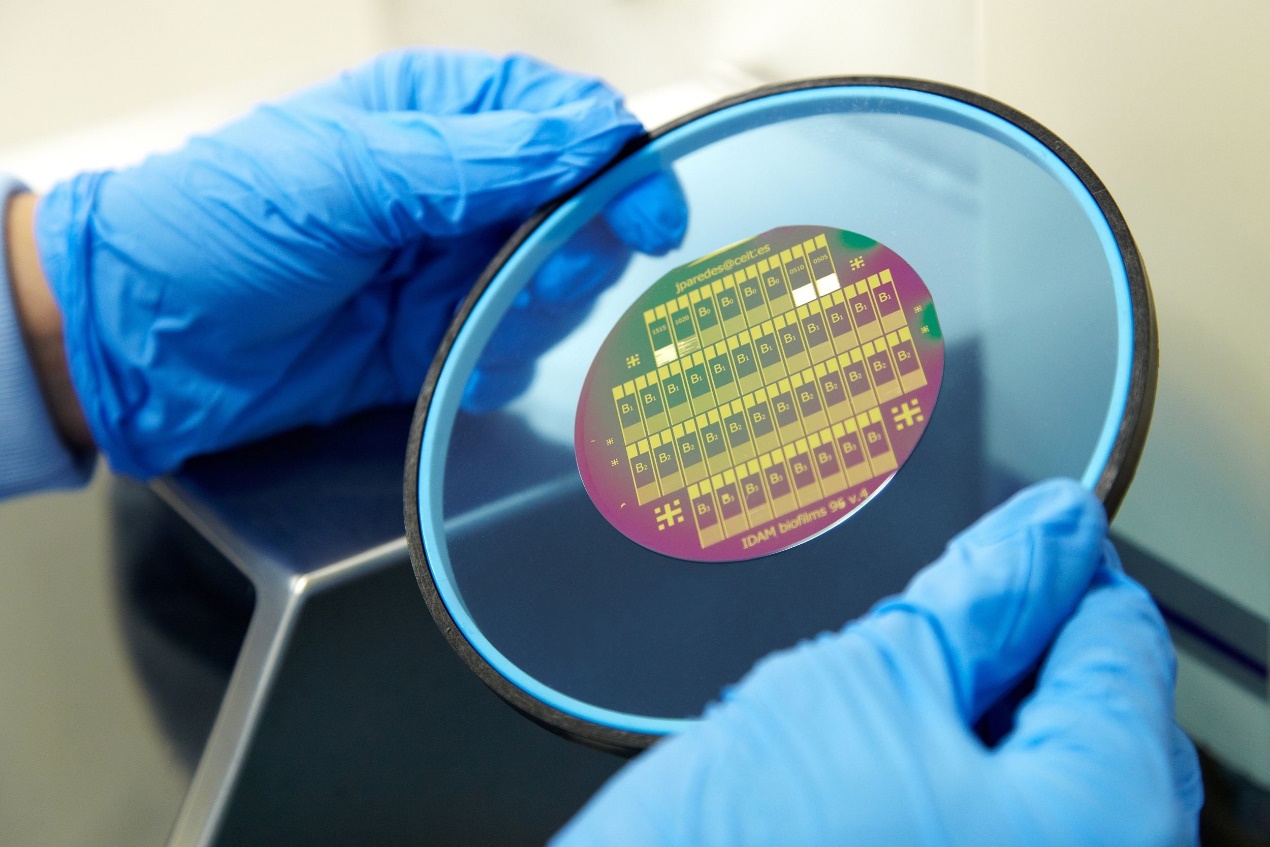

台积电CoWoS-S晶圆级封装技术针对高端市场,连线数量和封装尺寸都比较大,极大的突破了光刻掩膜尺寸的限制,芯片越做越大的今天,内部封装的小芯片也越来越多了,所以这也是台积电不断变强,成为全球第一大芯片代工厂的原因。

官方资料显示,台积电2016年就做到了1.5倍于掩模尺寸的规模,在单芯片内部能够实现4颗HBM高带宽内存芯片封装,2019年台积电又达成了2倍尺寸,6颗HBM芯片,并计划在2021年实现3倍尺寸、8颗HBM,2023年做到4倍尺寸,内部可封装多达12颗HBM。

按照这样的速度发展,加上主芯片13颗,HBM芯片12颗,意味着总面积估计可达到3200平方毫米。相比之下,性能强大的英伟达安培架构的GA100核心,其核心面积只有826平方毫米,不过这是7nm工艺下的极限了,可见台积电还要将面积提升4倍之多。

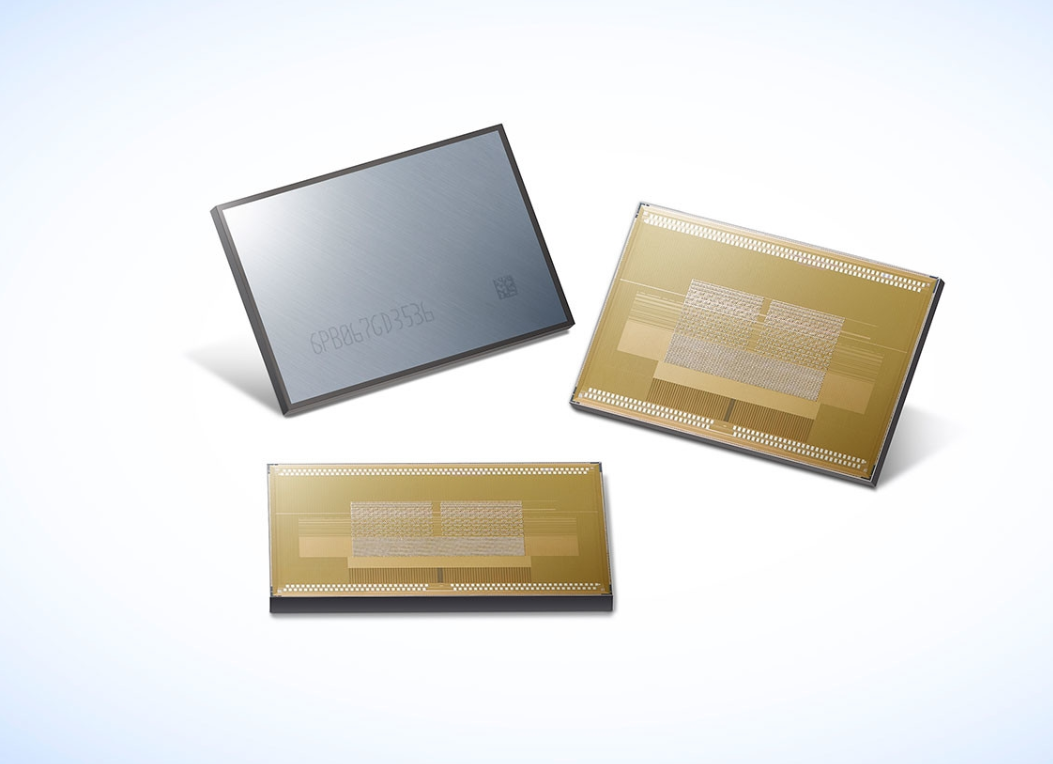

随着HBM显存技术的发展,未来无论是容量还是带宽都将超越很多人的想象,可能实现TB/s的速度都不是难题吧,目前三星HBM2e已经做到单颗12层堆叠,数据传输率3200MT/s,带宽至少4.92TB/s,速度相当惊人。

然而令人感到遗憾的是,台积电如此高级的封装技术华为可能彻底无缘了,因为按照禁令计划,9月15日之后华为芯片将无法由台积电代工生产,旗下高性能处理器同样将绝版,无论是对华为还是对中国,都是巨大的损失,不禁感叹一声,真的太可惜了!

打开微信扫一扫